![[Verilog HDL] 디설실 - 0. 논리회로 복습](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FYwKa9%2FbtssUNMTnIq%2FIs7pcqhZM1UgPuw6XKKLK1%2Fimg.webp)

[Verilog HDL] 디설실 - 0. 논리회로 복습CSE/Verilog HDL2023. 9. 4. 18:59

Table of Contents

소수점을 기준으로 한 숫자 시스템

- 숫자 시스템은 $r$을 밑(베이스)으로 해서 거듭 제곱 형태로 나타냄

10진수, 8진수, 16진수

- 10진수는 0부터 9까지

- 8진수는 0에서부터 7까지

- 16진수는 0에서부터 한 자리가 15까지 가질 수 있음

- 8진수는 특별한 목적이 아니면 잘 쓰지 않고 주로 2진수랑 16진수를 많이 씀

10진수와 2진수

10진수를 2진수로 변환

- 10진수를 0이 될 때까지 2로 계속 나눈 뒤 나머지를 역순로 읽기

2진수를 10진수로 변환

- 각 자릿수에 2의 거듭제곱을 곱함

- LSB에 $2^0$ 을 곱하고, MSB에 갈 수록 지수를 1씩 더함

보수(Complements)

- 보수는 디지털 컴퓨터에서 뺄셈 연산을 단순화하고 논리적 조작을 위해 사용됨

- 다시 말해, 이것은 음수를 표현하는 데 사용됨

- 각 base-r 시스템에는 두 가지 종류의 보수가 있음

- r의 보수

- (r-1)의 보수

- $N$이 정수 부분이 $n$자리인 기수 $r$에서 양수인 경우(소수 부분 없음)

- $N$의 $(r-1)$의 보수는 $(r^n-1) - N$임.

- 546700의 9의 보수는 999999 - 546700 = 453299

- 1011000의 1의 보수는 0100111

- $N$의 $r$의 보수는 $(r^n) - N$임. -> $(r-1)$의 보수 + 1

- 546700의 10의 보수는 1000000 - 546700 = 453300

- 1011000의 2의 보수는 0101000

이진수의 음수 표현

- 이진수를 음수로 나타내는 세 가지 방법

- 디지털 시스템은 일반적으로 2의 보수로 표현

2의 보수 산술

- 부호 비트가 부호를 나타냄

- 0: 양수

- 1: 음수

- MSB(가장 상위 비트)는 숫자의 부호 비트로 사용됨

- 덧셈

- 부호 비트를 포함한 두 숫자를 더함

- 부호 비트 위치의 자리올림을 무시함

- 뺄셈

- 뺄셈을 위해 피감수(빼려는 수)의 2의 보수를 취함. 이때 부호 비트를 포함

- 감산수(빼는 수)에 더함. 부호 비트를 포함.

- 부호 비트 위치의 자리올림을 무시함

문자 표현

- ASCII (American Standard Code for Information Interchange)

- 7비트를 사용하여 128개 문자를 인코딩함

- 52개 알파벳, 10개 숫자, 32개 특수 문자 및 34개 제어 문자를 포함함

부울 대수

- 부울 대수는 집합 B의 원소와 두 이항 연산자 +와 ·로 정의된 대수적 구조

- 두 값 부울 대수는 규칙을 가진 두 이항 연산자 + (OR)와 · (AND)로 정의됨

- 보수 연산자 ́(NOT)는 공리에 의해 검증됨

- 부울 대수의 연산자 우선순위는 (1) 괄호, (2) NOT, (3) AND, (4) OR임

- 부울 대수의 공리와 정리

디지털 논리 게이트

- 디지털 논리 게이트는 부울 대수를 기반으로 함

- AND, OR, Inverter, Buffer, NAND, NOR, XOR 및 XNOR 게이트를 포함

- 기호, 기능 및 진리 표

- 다중 입력 및 연쇄 논리 게이트

- NAND 및 NOR은 결합법칙이 성립하지 않음을 유의

- 연속적인 게이트는 다중 입력 게이트와 동일하지 않을 수 있음

부울 함수

- 부울 함수는 이전 변수, 상수 0과 1, 그리고 논리 연산 기호로 구성됨

- 2개의 변수에 대한 16개의 부울 함수

조합 회로

- 조합 회로는 논리 게이트의 상호 연결로 구성

- 입력 신호의 값을 감지하고 출력 신호의 값을 생성

- 주어진 데이터에서 필요한 출력 데이터로 이진 정보를 변환

- 조합 회로에는 피드백 경로나 메모리 요소가 없음

- n개의 입력 및 m개의 출력 조합 회로

- $2^n$개의 이진 입력 조합이 가능함

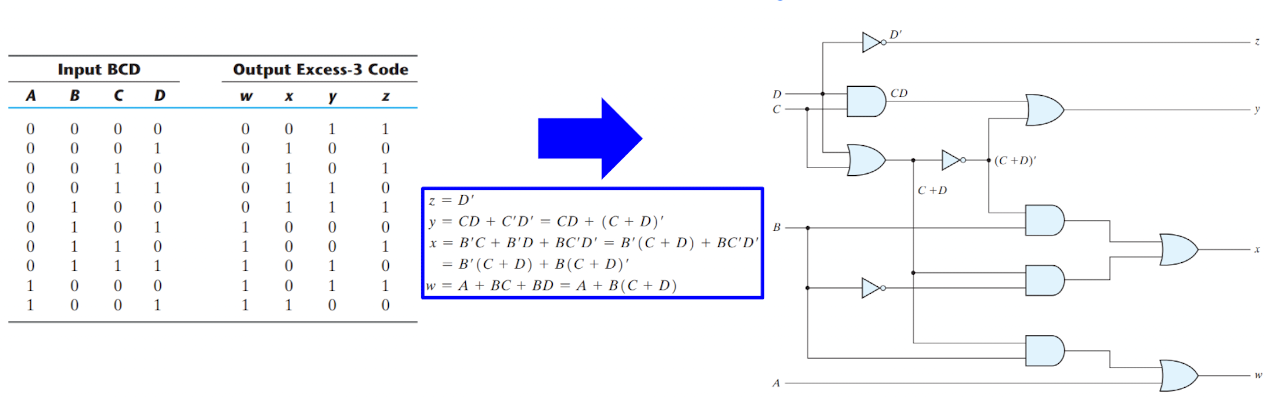

조합 회로 설계

- 조합 회로를 설계하는 절차

- 입력과 출력의 수를 결정

- 진리표를 도출함

- 각 출력에 대한 단순화된 부울 함수를 얻음

- 논리 다이어그램을 그리고 설계의 정확성을 확인함

- 예시 4개의 입력 (A, B, C, D) 및 4개의 출력 (w, x, y, z)

다양한 조합 회로

- 이진 덧셈-뺄셈기

- 이진 입력으로 덧셈 및 뺄셈을 수행함

- 디코더

- $n$-to-$2^n$ 디코더

- 예시) 011(3) → 00001000 (3번째 비트는 1이고 나머지는 0)

- 인코더

- $2^n$-to-$n$ 인코더

- 예시) 00001000→011

- 멀티플렉서

- $n$개의 입력 중 선택 신호에 따라 1개의 출력을 선택함

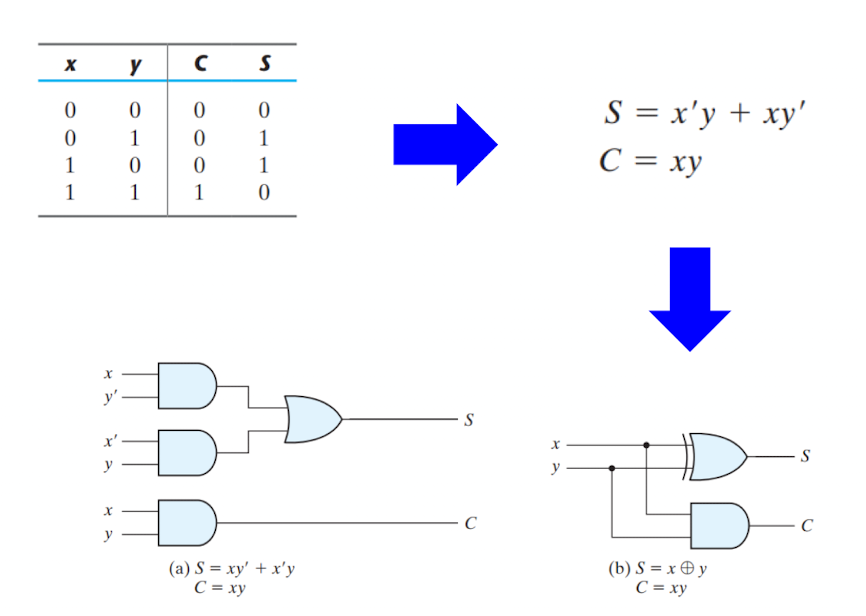

이진 덧셈-뺄셈기

- 반가산기

- 두 입력 x와 y로 합 (S)과 자리올림 (C)을 생성함

- 이진 덧셈기는 두 이진 숫자의 산술 합을 생성하는 디지털 회로

- 이를 연속된 전가산기로 구성할 수 있음

- 리플 캐리 덧셈기

디코더

n개의 입력 라인에서 이진 정보를 최대 $2^n$개의 고유한 출력 라인으로 변환함

3-to-8 라인 디코더

세 개의 입력 x, y, z가 여덟 개의 출력 $D_0$ ~ $D_7$로 디코딩됨

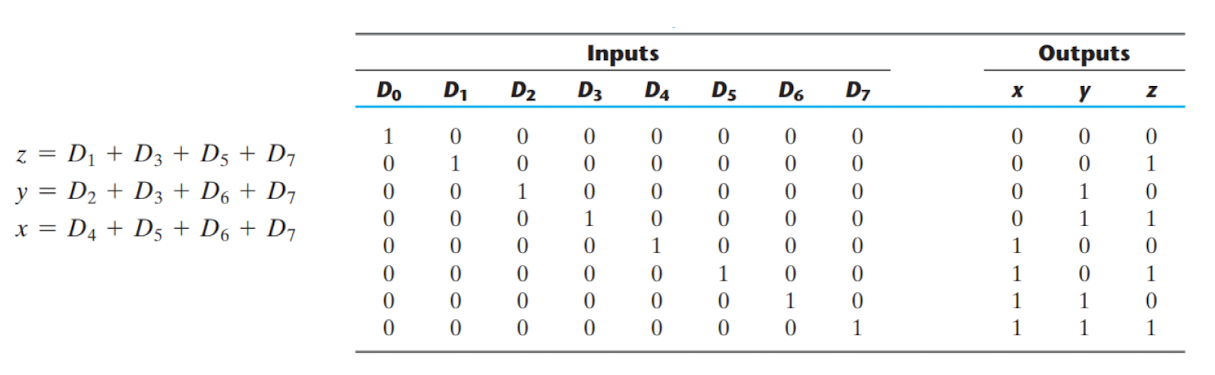

인코더

디코더의 역연산을 수행하는 디지털 회로

$2^n$개 (또는 그 이하)의 입력 라인과 $n$개의 출력 라인을 가지고 있음

8진법에서 이진법 인코더

인코더는 입력에 대한 진리표에서 직접 결정된 OR 게이트로 구현할 수 있음

멀티플렉서

- 여러 입력 라인 중 하나의 이진 정보를 선택하고 단일 출력 라인으로 보냄

- 특정 입력을 선택하는 것은 선택 라인의 집합에 의해 제어됨

- 보통 $2n$개의 입력 라인과 $n$개의 선택 라인이 있으며, 비트 조합이 어떤 입력이 선택되는지 결정함

- 2-to-1 멀티플렉서

- 4-to-1 멀티플렉서

- 4개의 입력 라인 ($I_0$, $I_1$, $I_2$, $I_3$)과 2개의 선택 라인 ($S_0$, $S_1$) → 1개의 출력

게이트 지연

- 실제로는 하나 이상의 입력 변경이 출력을 변경하는 경우, 출력 변경은 즉시 발생하지 않음

- 입력 변경과 결과 출력 변경 사이의 지연 (전파 지연이라고도 함)은 $t_G$로 표시되며 입력 변경과 결과 출력 변경 사이의 시간을 나타냄

순차 회로

- 메모리 요소가 연결되어 피드백 경로를 형성하는 조합 회로

- 메모리 요소는 이진 정보를 저장할 수 있는 장치

- 이러한 요소에 저장된 이진 정보는 순차 회로의 해당 시간에 대한 상태를 정의함

- 순차 회로는 입력, 출력 및 내부 상태의 시간 순서로 지정

- 반면, 조합 논리의 출력은 입력의 현재 값만에 따라 달라짐

동기 순차 회로

- 동기 순차 회로의 동작은 시간의 이산적인 순간에 대한 신호의 지식에서 정의될 수 있음

- 주기적인 클럭 펄스의 열을 생성하는 클럭 발생기라는 타이밍 장치가 포함됨

- 저장 요소 (Flip-Flop)는 각 클럭 펄스의 도착 시에만 영향을 받음

- 출력은 클럭 펄스의 존재하에서만 값을 변경할 수 있음

저장 요소

- 디지털 회로의 저장 요소는 입력 신호에 의해 상태 전환을 지시받을 때까지 이진 상태를 영구히 유지할 수 있음

- 래치

- 신호 전환보다 신호 수준과 함께 동작하는 저장 요소

- 레벨 감지 장치로 알려져 있음

- 플립플롭의 구성 요소

- 플립플롭 (FF)

- 클럭 전환에 의해 제어되는 저장 요소

- 엣지 감지 장치로 알려져 있음

- 동기 순차 회로에 유용함

SR 래치 - NOR 게이트 기반

- SR 래치는 두 개의 교차되는 NOR 또는 NAND 게이트와 S로 표시된 set 및 R로 표시된 reset 두 개의 입력이 있는 회로

- NOR 기반 SR 래치

- Set 상태: S=1, R=0→Q=1, Q ́=0

- Reset 상태: S=0, R=1→Q=0 및 Q ́=1

- 실제 응용에서는 두 입력을 모두 1로 설정하는 것이 금지되어 있음

- 상태를 변경해야 하는 경우를 제외하고는 두 입력 모두 0으로 유지됨으로써 래치는 상태를 유지

SR 래치 - NAND 기반

- NAND 기반 SR 래치 (S ́R ́ 래치)

- 입력은 NOR 래치에 사용된 것과 반대의 보수가 필요

- Set 상태: S=0, R=1 → Q=1, Q ́=0

- Reset 상태: S=1, R=0 → Q=0, Q ́=1

- 두 입력 모두 0인 경우가 금지되어 있음

- 래치의 상태를 변경해야 하는 경우를 제외하고는 두 입력 모두 정상적으로 1로 작동

제어 입력이 있는 SR 래치

- SR 래치의 동작은 상태를 언제 변경할 수 있는지를 결정하는 입력 신호를 추가함으로써 수정할 수 있음

- 제어 입력이 있는 SR 래치 기본 SR 래치와 두 개의 추가 NAND 게이트로 구성됨

- 제어 입력 En은 다른 두 입력에 대한 활성화 신호 역할을 함

- 두 개의 NAND 출력은 활성화 신호가 0으로 유지되는 한 논리 1로 유지됨

- 활성화 입력이 1로 변하면 S 또는 R 입력에서의 정보가 래치에 영향을 미치도록 허용

D 래치

- SR 래치의 바람직하지 않은 상태를 제거하는 한 가지 방법은 S와 R이 동시에 1이 되지 않도록 보장하는 것

- D 래치 (투명 래치)

- 두 개의 입력 D (데이터) 및 En (활성화)가 있으며 D 입력은 En = 1일 때 샘플링됨

- D 래치는 내부 저장 공간에 데이터를 보유할 수 있음

- En (활성화)가 asserted 될 때까지 출력은 D (데이터)의 변경 사항을 따름

- 출력에서 D로의 경로를 제공하기 때문에 투명한 래치로도 불림

래치와 플립-플롭의 클럭 응답

- 래치 또는 플립플롭의 상태는 제어 입력에 의해 전환됨

- 이 순간적인 변경을 트리거라고하며, 플립플롭/래치를 트리거한다고 함

- 래치의 문제는 클럭 펄스의 수준 변경에 응답한다는 것이 문제점

- enable input의 positive level response은 D 입력이 변경되는 동안 클럭 펄스가 논리 1로 유지될 때 출력 변경을 허용

- 플립플롭의 올바른 동작의 핵심은 래치를 시계열 회로의 피드백 경로를 제거하여 시계열 변화 중에만 트리거하도록 하는 것입니다.

Edge-Triggered D 플립-플롭

- D 플립플롭은 두 개의 D 래치와 인버터를 사용하여 구현됨

- D 입력을 샘플링하고 출력 Q를 동기화 또는 제어 클럭 Clk의 음의 에지에서만 변경함 (즉, 음의 에지 트리거된 FF).

- Clk = 1 → Master 활성화 (Y = D) 및 Slave 비활성화 (Q = 값 유지)

- Clk = 0 → Master 비활성화 (Y = 값 유지), Slave 활성화 (Q = Y)

- 플립플롭의 출력 변경은 클럭이 1에서 0으로의 전환 중에만 트리거될 수 있음

- 추가 인버터를 사용하면 플립플롭의 positive edge trigger로 만들 수 있음

클록 동기식 순차 회로의 분석

- 클록 동기식 순차 회로의 동작은 입력, 출력 및 플립플롭의 상태에서 결정됨

- 출력과 다음 상태는 입력과 현재 상태의 함수

- 순차 회로의 분석은 입력, 출력 및 내부 상태의 시간 순서를 나타내는 표나 다이어그램을 얻는 것으로 구성됨

- 논리 다이어그램은 클럭 입력이 있는 플립-플롭을 포함하고 있다면 클록 동기식 회로로 인식됨

- 논리 다이어그램에는 조합 논리 게이트가 포함되거나 포함되지 않을 수 있음

- 플립플롭은 어떤 유형이든 될 수 있음

- 상태 방정식, 상태 테이블 및 상태 다이어그램은 클록 동기식 순차 회로를 분석하는 데 사용될 수 있음

상태 방정식

- 상태 방정식(전이 방정식이라고도 함)은 현재 상태와 입력에 대한 함수로 다음 상태를 지정

- 두 개의 D 플립플롭 $(A, B)$ 및 입력 $x$와 출력 $y$

- 상태 방정식

- $A(t+1) = A(t)x(t) + B(t)x(t)$

- $B(t+1) = A ́(t)x(t)$

- $y(t) = [A(t) + B(t)]x ́(t)$

- 방정식의 왼쪽 부분인 t+1을 가진 부분은 클록 엣지 한 개 뒤의 플립플롭의 다음 상태를 나타냄

- $A(t+1) = Ax + Bx, B(t+1) = A ́x

- y = (A+B)x ́$

상태 테이블

- 상태 테이블(전이 테이블이라고도 함)은 현재 상태, 입력, 다음 상태 및 출력으로 구성

- 현재 상태와 입력의 모든 가능한 이진 조합을 나열

- $A(t+1) = Ax + Bx, B(t+1) = A ́x$

- $y = (A+B) x ́$

상태 다이어그램

- 상태 테이블은 상태 다이어그램 형태로 그래픽으로 나타낼 수 있음

- 원: 상태

- 선: 전이

- 입력/출력

728x90

반응형

@junyeokk :: 나무보다 숲을

컴퓨터 전공 관련, 프론트엔드 개발 지식들을 공유합니다. React, Javascript를 다룰 줄 알며 요즘에는 Typescript에도 관심이 생겨 공부하고 있습니다. 서로 소통하면서 프로젝트 하는 것을 즐기며 많은 대외활동으로 개발 능력과 소프트 스킬을 다듬어나가고 있습니다.

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!